一、什么是數字芯片?

數字芯片,是現代電子產品的“大腦”和“心臟”。它是一種集成電路,內部包含數百萬甚至數十億個微型晶體管,專門用于處理、存儲和傳輸離散的二進制信號(即0和1)。與處理連續模擬信號(如聲音、溫度)的模擬芯片不同,數字芯片處理的是數字邏輯運算,執行計算、邏輯判斷、數據存儲與控制指令等任務。

其核心工作原理基于布爾代數和門電路(如與門、或門、非門)。這些基本單元組合成復雜的邏輯功能模塊,如算術邏輯單元(ALU)、寄存器、存儲器陣列等,進而構成我們熟知的中央處理器(CPU)、圖形處理器(GPU)、內存(DRAM)、以及各種專用芯片(ASIC)。從智能手機、個人電腦,到數據中心服務器、自動駕駛汽車,幾乎所有智能設備的運行都離不開數字芯片的驅動。

二、數字芯片的技術與設計開發流程

數字芯片的誕生是一個極其復雜和精密的系統工程,主要分為前端設計和后端實現兩大階段:

- 前端設計(邏輯設計):

- 規格定義:根據產品需求(如性能、功耗、功能)確定芯片的頂層架構。

- 硬件描述語言(HDL)編碼:設計工程師使用Verilog或VHDL等語言,將功能描述轉化為寄存器傳輸級(RTL)代碼。

- 邏輯綜合:利用電子設計自動化(EDA)工具,將RTL代碼轉換為由基本邏輯門組成的網表。

- 功能驗證:通過仿真和形式驗證等方法,確保設計在邏輯上完全正確。

- 后端設計(物理設計):

- 布局規劃:規劃芯片上各個功能模塊的位置。

- 布線與時鐘樹綜合:連接所有邏輯單元,并分布時鐘信號以確保同步。

- 物理驗證與簽核:進行設計規則檢查(DRC)、電氣規則檢查(ERC)等,確保設計可以被成功制造。

- 流片與制造:將最終的設計數據(GDSII文件)交付給晶圓代工廠(如臺積電、三星),通過光刻、刻蝕、離子注入等數百道工序在硅片上制造出來。

整個流程高度依賴先進的EDA軟件、精密的制造工藝(如當前的3nm、2nm)和龐大的設計團隊協作。

三、數字芯片行業發展前景解析

數字芯片行業正處于一個波瀾壯闊、機遇與挑戰并存的歷史性時期,其發展前景可以從以下幾個維度解析:

- 核心驅動力:萬物智能與數字化浪潮

- 人工智能與高性能計算:ChatGPT等大模型的爆發,對GPU、AI專用芯片(如NPU、TPU)產生了海量需求,驅動算力芯片持續向更高性能、更低功耗演進。

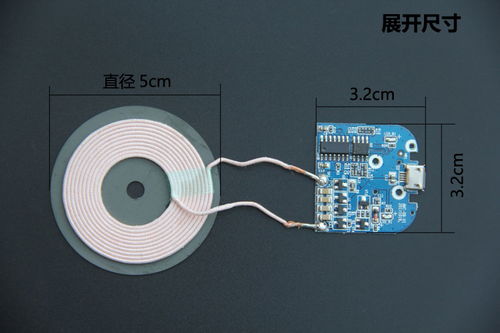

- 5G/6G與萬物互聯:通信技術的迭代需要大量的基帶芯片、射頻芯片,并將連接從手機擴展到海量的物聯網設備,催生對低功耗、高集成度邊緣計算芯片的需求。

- 汽車智能化:自動駕駛(感知、決策)和智能座艙的普及,使汽車正成為“輪子上的超級計算機”,對車規級SoC(系統級芯片)的需求呈指數級增長。

- 元宇宙與AR/VR:虛擬世界的構建與沉浸式體驗,對圖形渲染、空間計算和傳感器融合芯片提出了新的要求。

- 技術演進趨勢

- 延續摩爾定律與超越摩爾:一方面,通過3D封裝(如Chiplet小芯片技術)、先進制程(2nm及以下)繼續提升集成度與性能;另一方面,通過異構集成(將不同工藝、功能的芯片封裝在一起)、新材料(如GaN、SiC)探索新的發展路徑。

- 架構創新:從通用計算走向領域專用架構,針對AI、圖形、網絡等特定任務設計芯片,以獲得極致的能效比。開源指令集(如RISC-V)也為芯片設計帶來了新的靈活性和生態活力。

- 設計方法學革新:EDA工具向更高層次的抽象和智能化(AI for EDA)發展,以應對設計復雜度爆炸的挑戰。

- 挑戰與機遇并存

- 地緣政治與供應鏈安全:全球半導體產業鏈的局部脫鉤風險,促使主要經濟體(如中國、美國、歐盟)將芯片產業提升至國家戰略高度,投入巨資構建自主可控的供應鏈,這為本土設計、制造、設備和材料企業帶來了前所未有的歷史機遇。

- 技術壁壘與人才短缺:先進工藝研發成本攀升至百億美元級別,且需要頂尖的跨學科人才,構成了極高的行業壁壘。培養和吸引高端人才是行業持續發展的關鍵。

- 市場應用多元化:市場從消費電子“一枝獨秀”轉向“多極驅動”(汽車、工業、數據中心、AI),為芯片企業提供了更廣闊和差異化的賽道。

結論

數字芯片是數字經濟的基石,其發展直接決定了未來科技創新的高度與速度。當前,行業在AI、汽車電子等新動能驅動下,正步入一個技術快速迭代、應用百花齊放、全球格局重塑的黃金發展期。對于參與電子產品設計與技術開發的企業和個人而言,深入理解數字芯片的核心技術,并把握其向高性能、高能效、領域專用化發展的趨勢,將是構筑未來競爭力的關鍵所在。